- 您现在的位置:买卖IC网 > Sheet目录3871 > PIC18F84J11T-I/PT (Microchip Technology)IC PIC MCU FLASH 8KX16 80TQFP

2010 Microchip Technology Inc.

DS39774D-page 13

PIC18F85J11 FAMILY

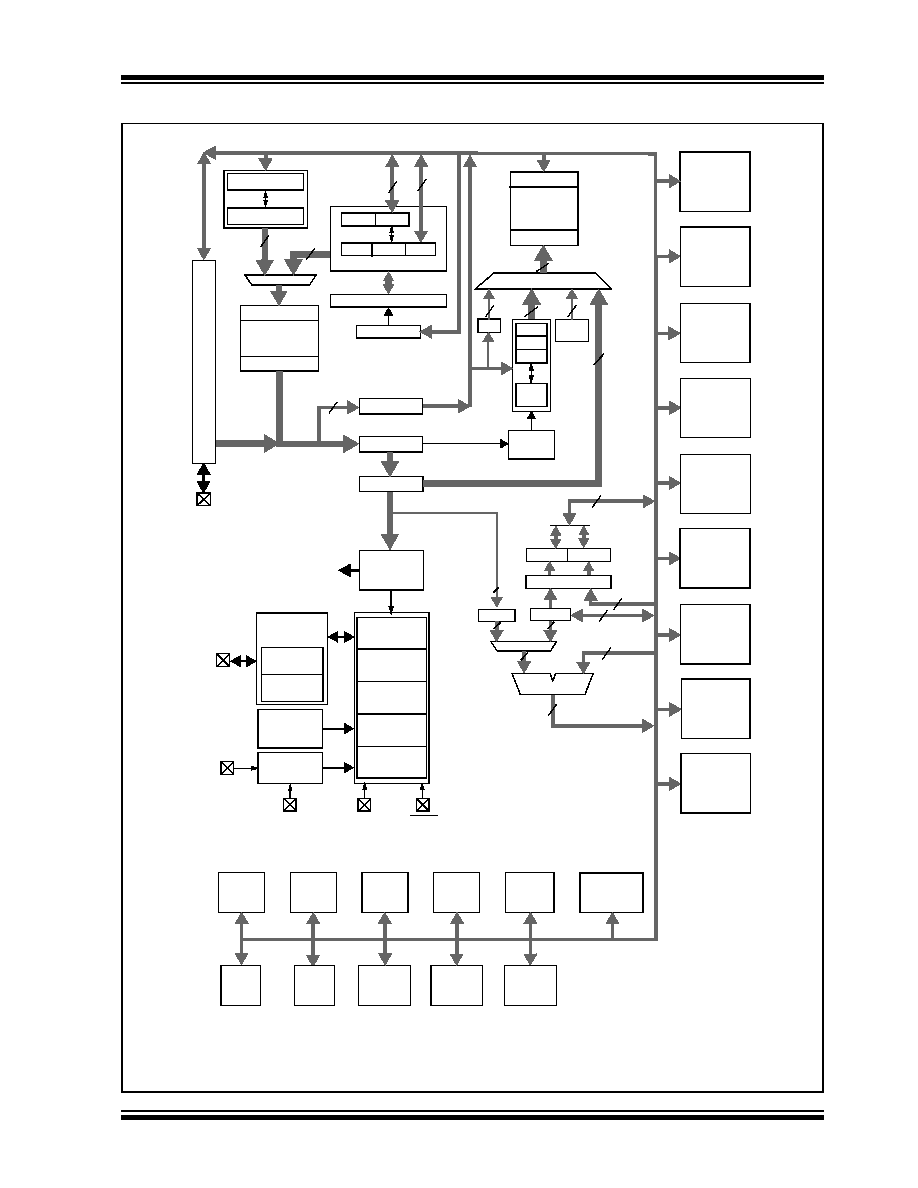

FIGURE 1-2:

PIC18F8XJ11 (80-PIN) BLOCK DIAGRAM

PRODL

PRODH

8 x 8 Multiply

8

BITOP

8

ALU<8>

8

3

W

8

Instruction

Decode &

Control

Data Latch

Data Memory

(3.9 Kbytes)

Address Latch

Data Address<12>

12

Access

BSR

FSR0

FSR1

FSR2

inc/dec

logic

Address

4

12

4

PCH

PCL

PCLATH

8

31 Level Stack

Program Counter

Address Latch

Program Memory

(128 Kbytes)

Data Latch

20

Table Pointer<21>

inc/dec logic

21

8

Data Bus<8>

Table Latch

8

IR

12

ROM Latch

PCLATU

PCU

Instruction Bus <16>

STKPTR

Bank

State Machine

Control Signals

Decode

S

yste

m

B

u

s

In

ter

face

AD15:AD0, A19:A16

(Multiplexed with PORTD,

PORTE and PORTH)

PORTA

PORTC

PORTD

PORTE

PORTF

PORTG

RA0:RA7(1,2)

RC0:RC7(1)

RD0:RD7(1)

RE0:RE7(1)

RF1:RF7(1)

RG0:RG4(1)

PORTB

RB0:RB7(1)

PORTH

RH0:RH7(1)

PORTJ

RJ0:RJ7(1)

AUSART

Comparators

MSSP

Timer2

Timer1

Timer3

Timer0

CCP1

ADC

10-Bit

EUSART

CCP2

OSC1/CLKI

OSC2/CLKO

VDD,VSS

MCLR

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Precision

Reference

Band Gap

Regulator

Voltage

VDDCORE/VCAP

ENVREG

Timing

Generation

INTRC

Oscillator

8 MHz

Oscillator

BOR and

LVD(3)

Note 1:

See Table 1-3 for I/O port pin descriptions.

2:

RA6 and RA7 are only available as digital I/O in select oscillator modes. See Section 3.0 “Oscillator Configurations” for more

information

3:

Brown-out Reset and Low-Voltage Detect functions are provided when the on-board voltage regulator is enabled.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F24K22-I/SP

IC PIC MCU 16KB FLASH 28SPDIP

PIC18LF25K22-I/SO

MCU 8BIT 32KB FLASH 3.6V 28SOIC

PIC18F83J90T-I/PT

IC PIC MCU FLASH 4KX16 80TQFP

PIC18LF24K22-I/SP

IC PIC MCU 16KB FLASH 28SPDIP

PIC32MX110F016B-I/SS

IC MCU 32BIT 16KB FLASH 28SSOP

PIC18F85J50T-I/PT

IC PIC MCU FLASH 16KX16 80TQFP

PIC18F45J10-I/P

IC PIC MCU FLASH 16KX16 40DIP

PIC24FJ16GA002-I/SO

IC PIC MCU FLASH 16K 28-SOIC

相关代理商/技术参数

PIC18F84J90-I/PT

功能描述:8位微控制器 -MCU 16KB Flash 1024bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F84J90T-I/PT

功能描述:8位微控制器 -MCU 16KB Flash 1024bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F8520-E/PT

功能描述:8位微控制器 -MCU 32KB 2048 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F8520-I/PT

功能描述:8位微控制器 -MCU 32KB 2048 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F8520-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F8520 TQFP80

PIC18F8520-I/PTG

功能描述:8位微控制器 -MCU 32KB 2048 RAM 68I/O Lead Free Package RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F8520T-E/PT

功能描述:8位微控制器 -MCU 40MHz 32KB Flash RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F8520T-I/PT

功能描述:8位微控制器 -MCU 32KB 2048 RAM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT